04. 10. 2021.

Komplementarni projekt u sklopu EuroHPC programa, Inicijativa za Europski procesor, još je jedan korak bliže demonstraciji sposobnosti RISC-V europskog mikroprocesora.

Inicijativa za Europski procesor (EPI), projekt s 28 partnera iz 10 europskih zemalja, s ciljem postizanja neovisnosti EU-a u tehnologiji HPC čipova i HPC infrastrukturi, objavio je da su uzorci testnih čipova EPAC1.0 RISC-V isporučeni EPI konzorciju te da su početna ispitivanja njihova rada bila uspješna.

Jedan od ključnih segmenata aktivnosti projekta je razvoj europskog intelektualnog vlasništva procesora temeljenih na RISC-V arhitekturi, koji omogućuju energetski učinkovite i visokopropusne jezgre akceleratora pod nazivom EPAC (European Processor Accelerators).

EPAC kombinira nekoliko akceleratorskih tehnologija specijaliziranih za različita područja primjene. Testni čip sadrži četiri jezgre za vektorsku obradu podataka (VPU) sastavljene od Avispado RISC-V jezgre te jedinice za vektorsku obradu podataka, u čijem dizajnu je sudjelovala i jedna članica Hrvatskog centra kompetencija za HPC – Fakultet elektrotehnike i računarstva Sveučilišta u Zagrebu. Čip sadrži i Home Node i L2 predmemoriju i dva dodatna akceleratora: Stencil i Tensor akcelerator (STX) te procesor promjenjive preciznosti (VRP). Svi akceleratori povezani su vrlo brzom mrežom na čipu i SERDES.

EPAC testni čipovi (njih 143) izrađeni su u GLOBALFOUDNRIES 22FDX tehnologiji male snage, imaju površinu od 26,97 mm2, 14 milijuna logičkih instanci (ekvivalentno 93M logičkih vrata) uključujući 991 memorijske instance, pakirani su u FCBGA s 22x22 matricom i imaju ciljanu frekvenciju od 1 GHz.

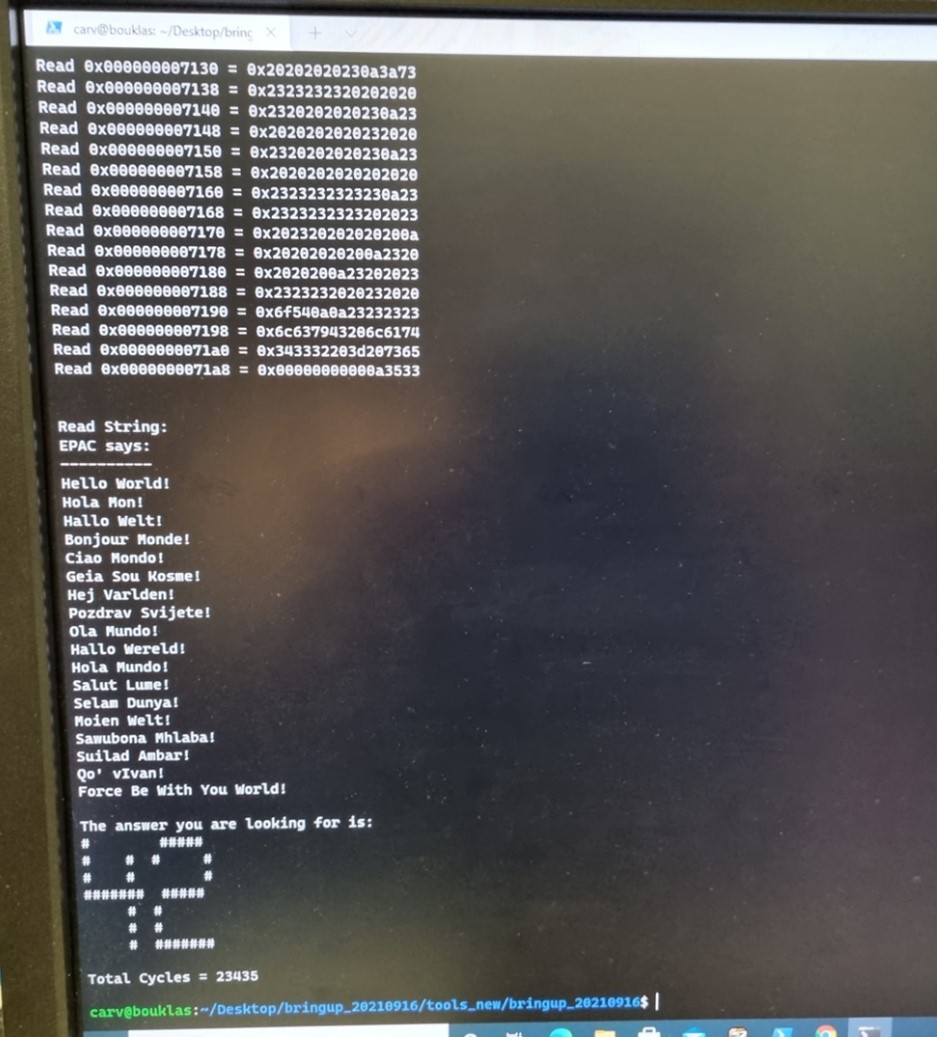

Inicijalno pokretanje bilo je uspješno, a EPAC je izveo svoj prvi program slanjem tradicionalnog “Pozdrav Svijete!” pozdrava na različitim jezicima EPI konzorciju i svijetu!

Inicijativa za Europski procesor (EPI) je projekt koji se provodi u okviru prve faze Okvirnog sporazuma o partnerstvu koji je konzorcij potpisao s Europskom komisijom, a čiji je cilj osmisliti i implementirati strategiju za nove generacije europskih procesora male snage za ekstremno računarstvo visokih performansi, Big-Data i brojne nove aplikacije.

EPI će nastaviti razvijati, optimizirati i potvrđivati različite IP blokove stvarajući EU HPC IP ekosustav i čineći ga dostupnim industriji i istraživačkim institucijama koji rade na procesorima i akceleratorima za stvaranje globalno konkurentnih modula za HPC sustave sljedećih generacija.